electronique-news.com

10

'26

Written on Modified on

Siemens coopère avec Nvidia à la vérification des puces d’IA

En combinant le prototypage basé sur FPGA avec une infrastructure de vérification évolutive, Siemens et Nvidia souhaitent valider des conceptions de plus en plus complexes dans des délais réalistes.

www.siemens.com

La conception de semi-conducteurs, le développement de systèmes sur puce (SoC) d’IA/ML et la vérification des systèmes électroniques nécessitent de plus en plus des méthodes de validation évolutives pour gérer la complexité croissante des architectures et des logiciels. Dans ce contexte, Siemens, en collaboration avec Nvidia, a fait progresser les capacités de vérification assistée par matériel afin de prendre en charge une validation à l’échelle de trillions de cycles au stade pré-silicium.

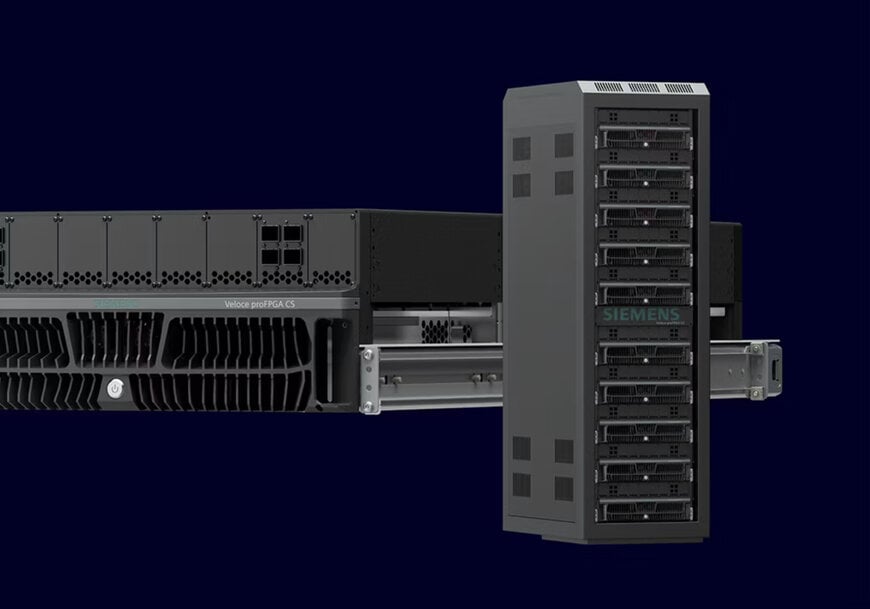

Le développement repose sur la plateforme Veloce proFPGA CS de Siemens, combinée aux architectures de puces optimisées pour les performances de Nvidia, permettant aux concepteurs d’exécuter et de capturer des dizaines de trillions de cycles de vérification en quelques jours.

Extension de la vérification au-delà des limites traditionnelles

À mesure que la complexité des SoC d’IA/ML augmente, les charges de travail de vérification se sont considérablement étendues, sous l’effet des architectures matérielles et des exigences des piles logicielles. Les approches de vérification conventionnelles telles que la simulation et l’émulation traitent généralement des millions à quelques milliards de cycles dans des délais pratiques, créant des goulets d’étranglement dans le développement.

L’utilisation de systèmes de prototypage basés sur FPGA permet d’exécuter ces charges de travail beaucoup plus rapidement en exécutant les conceptions sur du matériel plutôt que uniquement dans des modèles logiciels. Avec le système Veloce proFPGA CS, cette approche s’étend à des trillions de cycles, permettant des scénarios de validation auparavant impraticables.

Prototypage basé sur FPGA pour les systèmes d’IA/ML

La plateforme Veloce proFPGA CS est conçue pour fournir une architecture matérielle évolutive et flexible pour la validation d’IP sur FPGA unique ainsi que pour des conceptions de chiplets comportant plusieurs milliards de portes. En intégrant les architectures de puces de Nvidia, le système prend en charge l’exécution de charges de travail à grande échelle, permettant aux ingénieurs de valider le comportement fonctionnel et les performances du système avant la fabrication du silicium.

Cette capacité est particulièrement pertinente pour les applications d’IA/ML, où les charges de travail sont intensives en données et nécessitent une validation approfondie afin de garantir la fiabilité et les performances dans des conditions réelles.

Impact sur les délais de développement et la fiabilité

L’exécution de trillions de cycles de vérification en peu de temps permet de détecter plus tôt les problèmes de conception, réduisant ainsi le risque de reconceptions coûteuses après la fabrication. Cela contribue à réduire les délais de mise sur le marché tout en maintenant les normes de fiabilité requises pour les dispositifs semi-conducteurs avancés.

Selon Nvidia, la capacité de valider des charges de travail à grande échelle apporte de la confiance dans les architectures d’IA de nouvelle génération, en particulier à mesure que les systèmes informatiques continuent d’évoluer en complexité.

Applications dans la conception avancée de semi-conducteurs

Cette approche de vérification est applicable à une gamme d’applications dans les semi-conducteurs, notamment les accélérateurs d’IA, les processeurs de centres de données et les systèmes de calcul haute performance. Dans ces domaines, il est essentiel de garantir un fonctionnement correct sous des charges de travail étendues avant de passer à la production.

Publié par Natania Lyngdoh, rédactrice pour Induportals — Adapté par IA.

www.siemens.com