electronique-news.com

16

'26

Written on Modified on

Des mémoires taillées pour les applications de calcul intensif à base d'IA

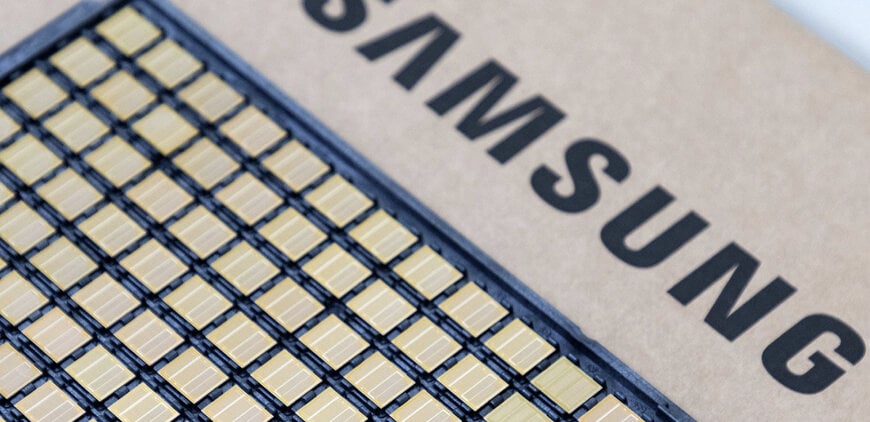

Samsung a lancé la production de masse et les livraisons commerciales des mémoires à très large bande passante de la gamme HBM4, conçue pour répondre aux exigences de l'IA et du calcul haute performance.

semiconductor.samsung.com

Cette génération de mémoire vise principalement les accélérateurs IA avancés et les infrastructures de centres de données.

Architecture mémoire pour charges de travail IA intensives

La série HBM4 constitue la quatrième génération de mémoire empilée à très large bande passante et s’attaque au phénomène dit de « memory wall », qui limite les performances des processeurs lorsque le débit mémoire devient insuffisant.

Les piles HBM4 reposent sur un procédé DRAM de sixième génération en classe 10 nm, associé à un die logique de base gravé en 4 nm. Cette combinaison permet d’améliorer les caractéristiques électriques, les rendements de fabrication et la montée en cadence industrielle.

En configuration standard, la mémoire HBM4 atteint une vitesse de transfert de 11,7 gigabits par seconde (Gb/s) par broche, au-dessus de la spécification JEDEC d’environ 8 Gb/s pour la HBM4, et environ 22 % plus rapide que la génération précédente HBM3E de Samsung. Des pointes pouvant atteindre 13 Gb/s sont annoncées dans certaines conditions d’exploitation.

Pour les systèmes d’entraînement et d’inférence IA, cela signifie une alimentation plus continue des unités de calcul et une meilleure utilisation des GPU ou accélérateurs spécialisés.

Bande passante et capacités mémoire accrues

Le doublement du nombre de broches d’E/S, passant de 1 024 à 2 048 connexions, permet d’atteindre une bande passante maximale d’environ 3,3 téraoctets par seconde (To/s) par pile, soit environ 2,7 fois celle de la HBM3E.

Les premières configurations comprennent des piles de 24 Go et 36 Go avec empilement TSV (Through-Silicon Via) à 12 couches. Une version de 48 Go à 16 couches est prévue. Ces capacités répondent aux besoins des grands modèles de langage, de l’IA générative et des simulations HPC, où la mémoire locale joue un rôle clé dans l’optimisation de l’écosystème de centre de données numérique.

Efficacité énergétique et gestion thermique

L’augmentation de la densité d’E/S entraîne des défis en matière d’alimentation électrique et de dissipation thermique. Samsung intègre des TSV basse tension et des réseaux de distribution d’alimentation optimisés pour réduire les pertes électriques.

Selon l’entreprise, la mémoire HBM4 offre une amélioration d’environ 40 % de l’efficacité énergétique par rapport à la HBM3E. Elle annonce également une résistance thermique accrue de 10 % et une dissipation thermique améliorée de 30 %, éléments essentiels pour garantir la stabilité opérationnelle des modules d’accélération IA à forte densité.

Stratégie industrielle et feuille de route

Samsung souligne l’intégration de ses activités mémoire et fonderie, ainsi que ses capacités avancées d’assemblage et de packaging, pour soutenir la montée en volume de la HBM4. Les capacités de production devraient être étendues en fonction de la demande croissante du marché IA.

Des échantillons de la génération suivante, de la série HBM4E, sont prévus pour le second semestre 2026. Des solutions HBM personnalisées sont également envisagées à partir de 2027.

www.samsung.com

Architecture mémoire pour charges de travail IA intensives

La série HBM4 constitue la quatrième génération de mémoire empilée à très large bande passante et s’attaque au phénomène dit de « memory wall », qui limite les performances des processeurs lorsque le débit mémoire devient insuffisant.

Les piles HBM4 reposent sur un procédé DRAM de sixième génération en classe 10 nm, associé à un die logique de base gravé en 4 nm. Cette combinaison permet d’améliorer les caractéristiques électriques, les rendements de fabrication et la montée en cadence industrielle.

En configuration standard, la mémoire HBM4 atteint une vitesse de transfert de 11,7 gigabits par seconde (Gb/s) par broche, au-dessus de la spécification JEDEC d’environ 8 Gb/s pour la HBM4, et environ 22 % plus rapide que la génération précédente HBM3E de Samsung. Des pointes pouvant atteindre 13 Gb/s sont annoncées dans certaines conditions d’exploitation.

Pour les systèmes d’entraînement et d’inférence IA, cela signifie une alimentation plus continue des unités de calcul et une meilleure utilisation des GPU ou accélérateurs spécialisés.

Bande passante et capacités mémoire accrues

Le doublement du nombre de broches d’E/S, passant de 1 024 à 2 048 connexions, permet d’atteindre une bande passante maximale d’environ 3,3 téraoctets par seconde (To/s) par pile, soit environ 2,7 fois celle de la HBM3E.

Les premières configurations comprennent des piles de 24 Go et 36 Go avec empilement TSV (Through-Silicon Via) à 12 couches. Une version de 48 Go à 16 couches est prévue. Ces capacités répondent aux besoins des grands modèles de langage, de l’IA générative et des simulations HPC, où la mémoire locale joue un rôle clé dans l’optimisation de l’écosystème de centre de données numérique.

Efficacité énergétique et gestion thermique

L’augmentation de la densité d’E/S entraîne des défis en matière d’alimentation électrique et de dissipation thermique. Samsung intègre des TSV basse tension et des réseaux de distribution d’alimentation optimisés pour réduire les pertes électriques.

Selon l’entreprise, la mémoire HBM4 offre une amélioration d’environ 40 % de l’efficacité énergétique par rapport à la HBM3E. Elle annonce également une résistance thermique accrue de 10 % et une dissipation thermique améliorée de 30 %, éléments essentiels pour garantir la stabilité opérationnelle des modules d’accélération IA à forte densité.

Stratégie industrielle et feuille de route

Samsung souligne l’intégration de ses activités mémoire et fonderie, ainsi que ses capacités avancées d’assemblage et de packaging, pour soutenir la montée en volume de la HBM4. Les capacités de production devraient être étendues en fonction de la demande croissante du marché IA.

Des échantillons de la génération suivante, de la série HBM4E, sont prévus pour le second semestre 2026. Des solutions HBM personnalisées sont également envisagées à partir de 2027.

www.samsung.com